Brevet : WO9812706 - DISPOSITIF ET PROCEDE D'ESSAI DES DES D'UN CIRCUIT INTEGRE DANS UN MODULE DE CI...

Titre

DISPOSITIF ET PROCEDE D'ESSAI DES DES D'UN CIRCUIT INTEGRE DANS UN MODULE DE CIRCUIT INTEGRE

N° et date de publication de la demande

WO9812706 - 26/03/1998

Type de la demande

A1

N° et date de dépôt

PCT/US9714564 - 20/08/1997

N° et date de priorité

US71817396 - 19/09/1996

Classification CIB

G01R 31/28 ; G11C 5/00 ; H01L 23/12 ; G11C 29/00 ; G11C 29/14 ; G11C 29/46 ; H01L 21/66 ; H01L 25/04 ; H01L 25/18 ; H04Q 11/04

Classification CPC

G01R 31/2884 ; G11C 29/46 ; G11C 29/785 ; G11C 29/80 ; G11C 29/808 ; H01L 22/22 ; H04J2203/0062 ; H01L2224/48091 ; G11C 29/00 ; H01L 22/22 ; G11C 29/785 ; G11C 29/80 ; H04J2203/0062 ; G01R 31/2884 ; G11C 29/46 ; G11C 29/808 ; H01L2224/48091

Famille de brevets

ATE208953T1 ; TW356576B ; JP2001500659A ; US5796746A ; KR20000048488A ; WO9812706A1 ; AU4074397A ; DE69708314T2 ; EP0928486A1

Abrégé

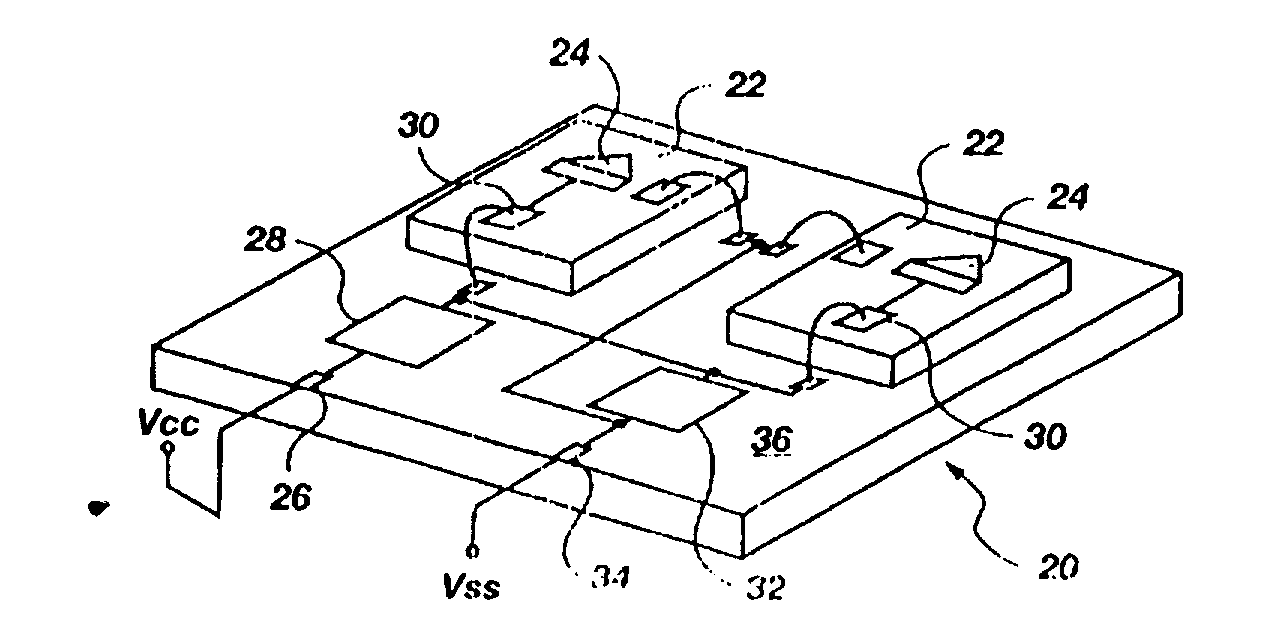

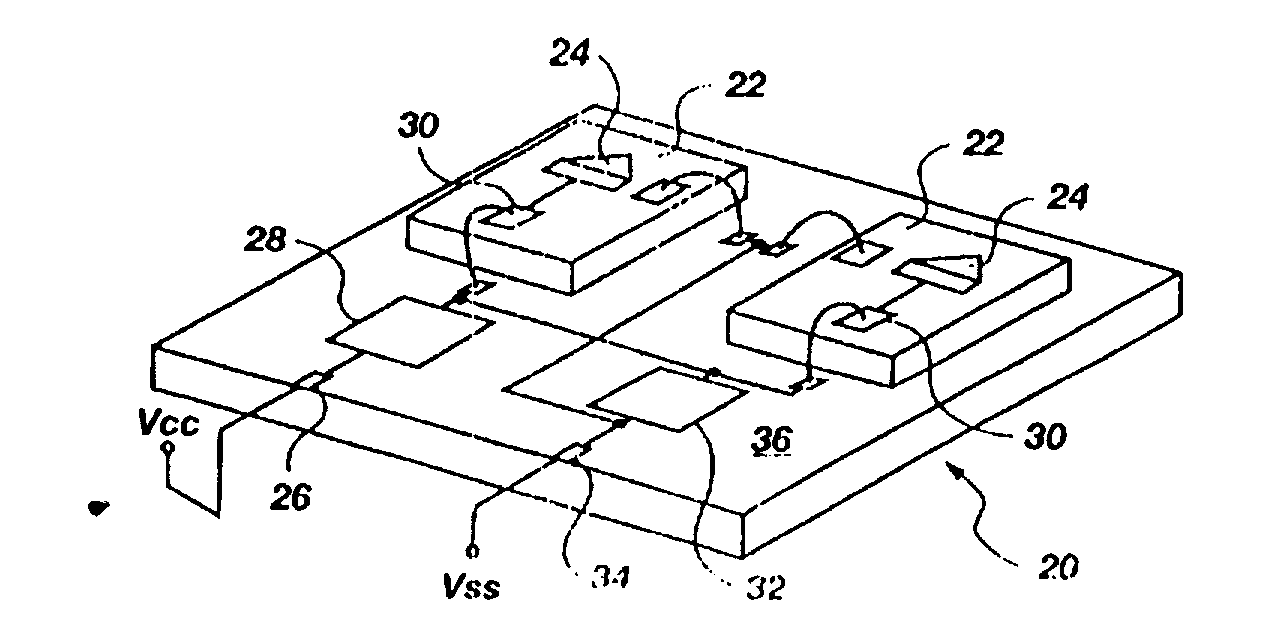

L'invention concerne un module (20) CI, par exemple un module multipuce (MMP), qui comprend de multiples dés CI (12) ayant chacun un plot (30) de connexion de validation de mode essai, tel qu'un plot de validation de sortie. Un fusible incorporé dans le substrat MMP connecte chaque plot de validation de mode essai de chaque dé à l'une des broches de non-connexion (N/C) du MMP, et une résistance incorporée dans le substrat connecte les plots de validation de mode essai à l'une des broches de tension de référence du MMP. En appliquant une tension d'alimentation aux plots de validation de mode essai à travers la broche N/C, un mode essai est activé sur les dés. Une fois l'essai achevé, le fusible peut être fondu, et une tension de référence appliquée aux plots de validation de mode essai à travers les broches de tension de référence. La résistance désactive alors le mode essai dans les dés et entame un mode opérationnel. En conséquence, les dés conditionnés dans les modules CI peuvent être essayés après conditionnement. L'invention concerne également un procédé de réalisation de ces essais une fois que le mode essai a été activé et de réparation des éléments défaillants au cours des essais. Ledit procédé consiste à émettre des signaux pour identifier un élément défaillant dans les dés, à programmer les adresses des éléments défaillants sous forme d'anti-fusibles dans les dés avec une tension de programmation et à confirmer que les adresses sont programmées en déterminant la résistance des anti-fusibles, en réessayant les dés, en recevant des signaux réponse à partir des dés réessayés et en évaluant les signaux réponse pour confirmer toutes les réparations.

INTERVENANTS

Déposant

MICRON TECHNOLOGY INC (MICRON TECHNOLOGY, INC.) - US

Inventeur

FARNWORTH WARREN M (FARNWORTH, WARREN, M.)

WARK JAMES M (WARK, JAMES, M.)

NELSON ERIC S (NELSON, ERIC, S.)

DUESMAN KEVIN G (DUESMAN, KEVIN, G.)