Brevet : WO2008155803 - DISPOSITIF ARITHMÉTIQUE POUR LE TRAITEMENT SIMULTANÉ D'UNE PLURALITÉ DE FILS

Titre

DISPOSITIF ARITHMÉTIQUE POUR LE TRAITEMENT SIMULTANÉ D'UNE PLURALITÉ DE FILS

N° et date de publication de la demande

WO2008155803 - 24/12/2008

Type de la demande

A1

N° et date de dépôt

PCT/JP2007000661 - 20/06/2007

N° et date de priorité

PCT/JP2007000661 - 20/06/2007

Classification CIB

Classification CPC

Famille de brevets

KR20100021455A ; EP2169553A1 ; JPWO2008155803A1 ; CN101681285A ; US2010088544A1 ; WO2008155803A1

Abrégé

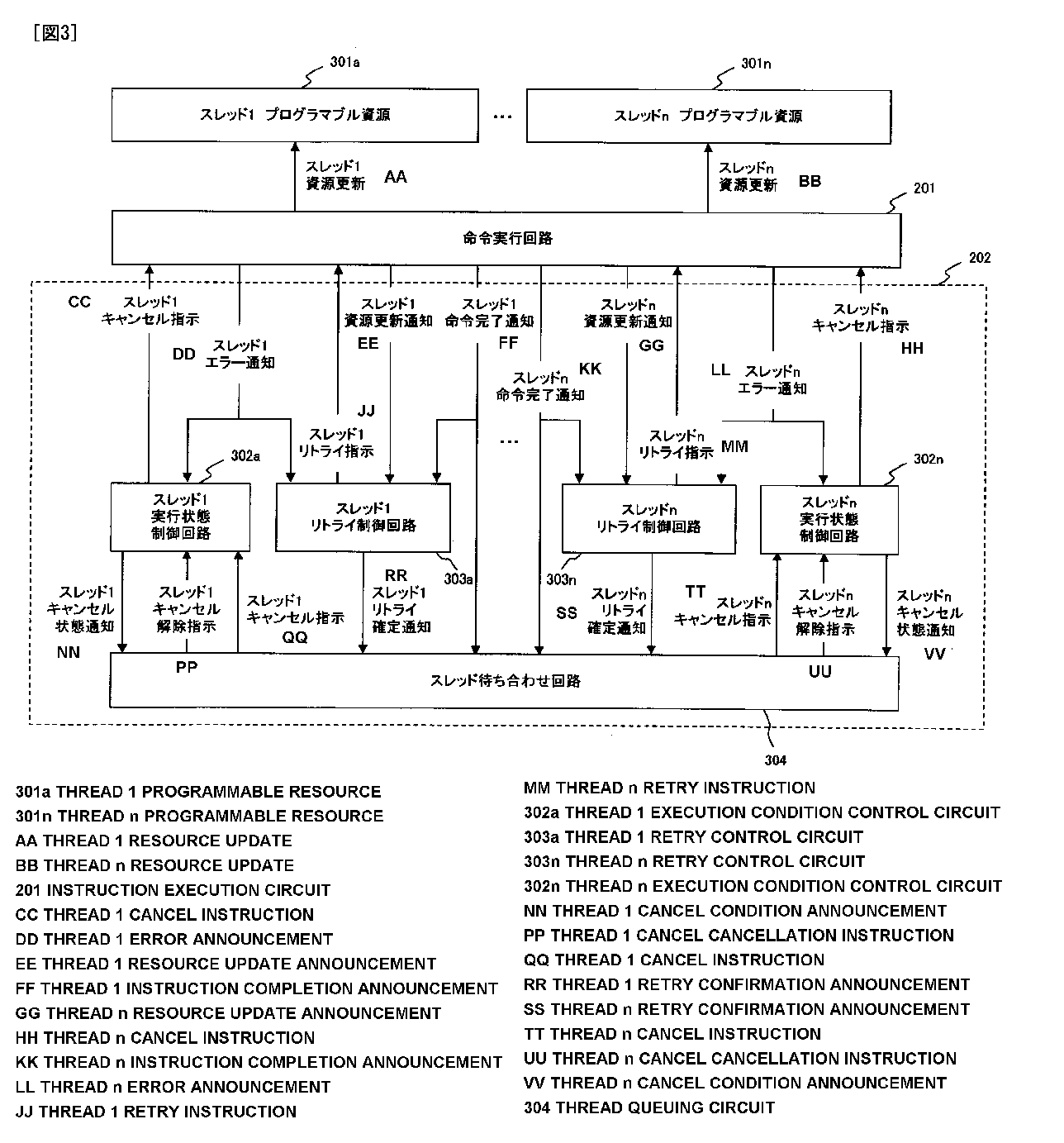

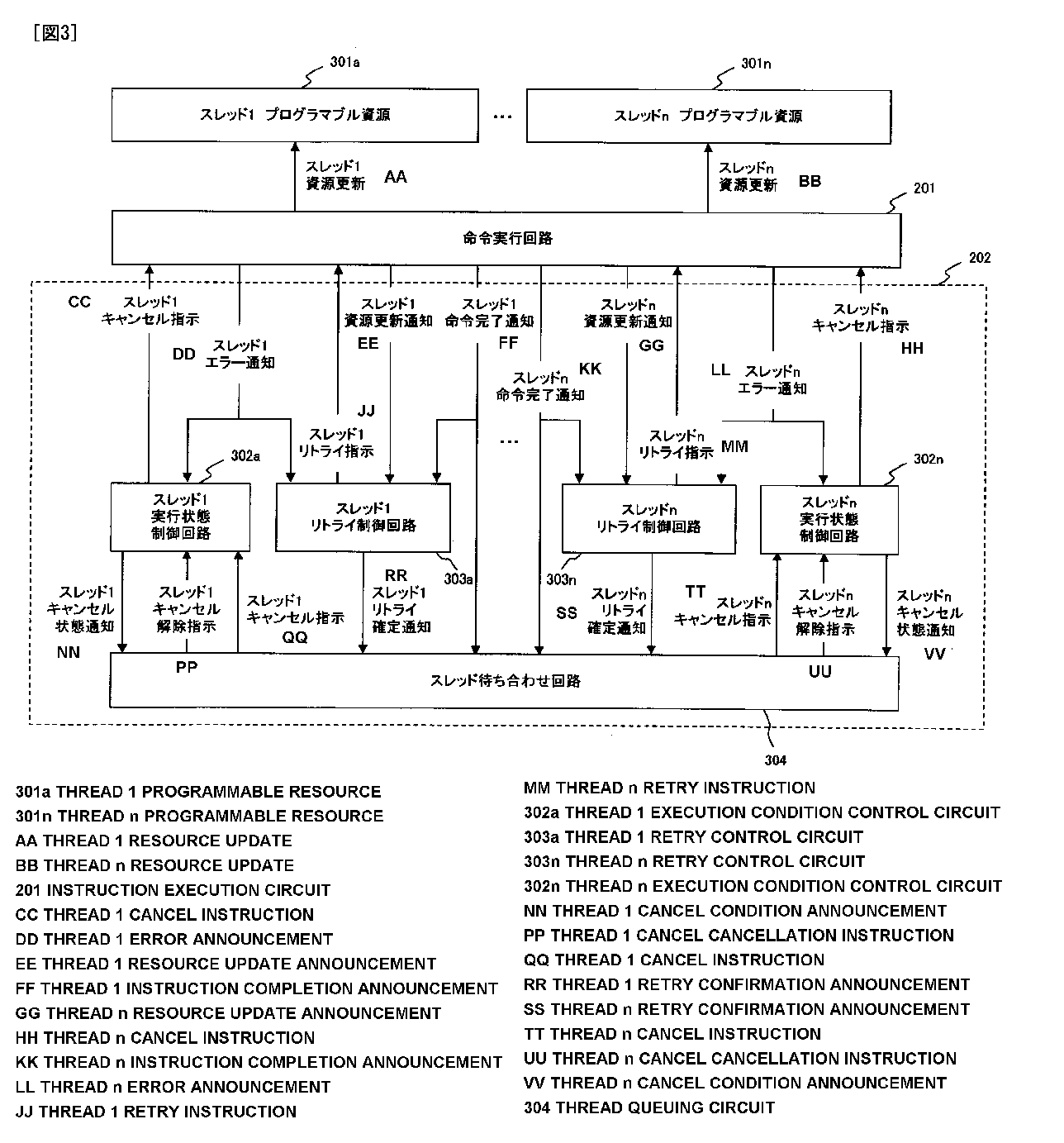

L'invention concerne un processeur capable de traiter simultanément des séquences d'instructions d'une pluralité de fils, qui réalise un taux de succès de relance similaire à celui d'un processeur pour traiter une séquence d'instructions d'un seul fil. Un dispositif arithmétique (200) comprend un circuit d'exécution d'instruction (201) pour exécuter la pluralité de fils et un circuit de commande d'exécution (202) pour commander des conditions d'exécution et une réexécution de chaque fil.

INTERVENANTS

Déposant

FUJITSU LTD (FUJITSU LIMITED) - JP

GOMYO NORIHITO (GOMYO, NORIHITO) - JP

SUNAYAMA RYUICHI (SUNAYAMA, RYUICHI) - JP

Inventeur

GOMYO NORIHITO (GOMYO, NORIHITO) - JP

SUNAYAMA RYUICHI (SUNAYAMA, RYUICHI) - JP